SOI高g值压阻式加速度传感器与工艺实现

基于SOI 技术,利用电感耦合等离子体硅深加工,设计制备了一种新型平面内振动高g 值压阻式加速度计。该加速度计包括X 轴向与Y 轴向单元,采用扇形敏感质量块平板内振动结构。对称的布局方式,有效地消除了灵敏度的交叉干扰,提高了传感器的测量精度。测试系统分析出加速度传感器的灵敏度是1.170 LV/ g 。研究表明该加速度传感器可实现对量程高达25× 104g 加速度的测量。

微机电系统( MEMS) 加速度传感器是一种重要的惯性测量器件,具有体积小、重量轻、响应快、易于加工等优点,目前已广泛应用于汽车、航空航天、军事等领域。其中高g 值加速度传感器在军事领域具有非常重要的应用价值,可以感知导弹的飞行状态、硬目标侵彻时产生的冲击力等。在具有较大惯性载荷的军用场合,需要测量的加速度高达几万甚至几十万加速度,这就要求加速度计不仅需要高的灵敏度,还要具有高的谐振频率与抗冲击能力。

目前中国在高g 值加速度计研究方面与国外还存在较大差距,由于国外该领域的技术封锁,迫切需要研发出可应用于动态撞击过程及高速运动过程中冲击载荷测量的高g 值加速度传感器。针对目前航空航天,特别是导弹引信等军事领域对高g 值加速度传感器的迫切需求,充分利用SOI 材料的抗辐射、抗高温等恶劣环境以及低功耗的特点,在前期研究的基础上,本文实际制备了二维平面内振动、基于SOI 硅片的高g 值压阻式加速度传感器。利用SOI 上层硅制作惠斯通电桥双U 型梁压敏电阻,同时避免了在可动部件上布线; 敏感元件、硅基底间采用高温介质层(SiO2 层) 实现电隔离,解决传统半导体传感器因制作过程中寄生PN 结漏电流而造成的温漂问题; 利用刚度较大的主悬臂梁和扇形敏感质量块,大大提高了结构的可靠性和灵敏度。前期模拟研究和本文的实验分析表明,设计的加速度计具有较高的灵敏度与谐振频率,具有较大的抗冲击能力,可满足特种环境下对高达25 ×104g 加速度的测试需求。

1、高g 值压阻式加速度传感器的结构与制备

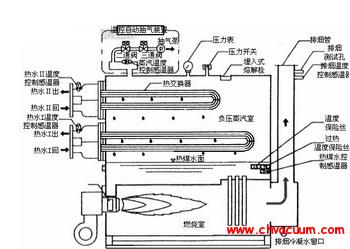

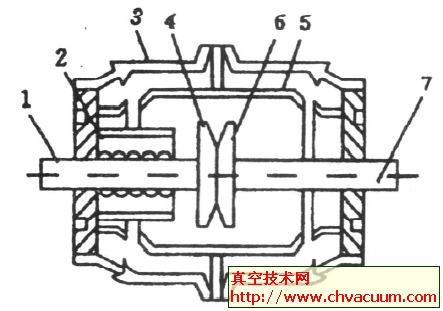

本文设计的二维平面内振动SOI 高g 值加速度传感器包括两两对应的四个单元。每一个结构单元由主悬臂梁、两个用于支撑U 型压敏电阻的侧微梁,扇形敏感质量块、两个双U 型压敏电阻和两个参考电阻构成惠斯通电桥组成,实际制备的传感器如图1 所示。

图1 SOI 高g 值压阻式加速度传感器

制备工艺过程需注意: 高温工艺的排序遵循: 先高温工艺,后低温工艺。金属化应放在所有可能是该金属融化或与其他材料共融的高温工艺之后。»光刻前,应保证硅片表面没有高深宽比的台阶。湿法腐蚀是否引入导致器件失效的杂质离子。材料的选择是否会造成加工设备的污染。该加速度传感器的加工制备只需五块掩膜板,实际制备工艺过程如下:

( 1) 备片: 准备一块双面抛光的SOI 硅片,下层硅厚度为300 um,SiO2 层厚度为1 um,上层p+ 硅厚度为2~ 3 um,电阻率为0.005~ 0. 008 欧姆.cm。

( 2) 初氧: 对SOI 硅片进行热氧化。

( 3) 匀胶、光刻( 一次光刻) : 在下层硅上旋涂正胶,利用第一块掩模板对光刻胶进行光刻、显影、后烘后再刻蚀氧化层,以氧化层作保护层,刻蚀下层硅,形成背面浅槽。刻蚀5 um 浅槽,为后续释放结构形成可动部件,该层版图是负版,同时把结构的划片槽打开。

( 4) 背面淀积铝层: 对上步硅片去胶清洗后,背面淀积金属铝层。

( 5) 背面深刻( 二次光刻) : 在上步工艺后的下层硅铝层上经过匀胶、前烘、光刻、显影和后烘后,对铝层进行刻蚀,再以铝层作为保护层,刻蚀下层硅,形成质量块。质量块与主悬臂梁,该层版图为负版,刻蚀区宽度为30 um。

( 6) 键合: 对上步硅片进行去胶、清洗、退水等处理后,利用键合技术,进行下层硅与玻璃的键合,完成下盖板的封装。

( 7) 重掺杂、三次光刻: 上层硅开孔。对上层硅进行重掺杂,形成欧姆接触区,开孔尺寸为8 um ×8um,该层掩模板为负版,与第二层板进行套刻,考虑到透光区域少,难对准,该层掩模板打开划片区。在上层硅进行匀胶、前烘,利用第三块掩模板进行光刻、显影、后烘等处理后,刻蚀氧化层,以氧化层作为保护层,进行B 离子的注入。

( 8) 金属引线刻蚀( 四次光刻) : 对上步硅片进行去胶、清洗等处理后,淀积一层金属铝,再进行匀胶,利用第四块掩模板进行光刻,进过后烘等一系列处理后,刻蚀金属铝,形成铝布线。其中金属线宽度最小为20 um,电极尺寸为200 um × 300 um,电极之间的间距为250 um,金属线之间的最小间距为14 um。该层板为正版,与第二层板进行套刻对准。

( 9) 压敏电阻条制作( 五次光刻) : 在上步硅片正面旋涂一层光刻胶,利用第五块掩模板进行光刻,经过显影后烘后,刻蚀上层硅片,形成压敏电阻区。为了有效地减小金属电极引入的电阻,与上步工艺的结合,同时简化加工难度,上层硅大部分处于保留,其中在质量块周围的上层硅多偏离背面深槽5 um,确保结构释放时形成可动部件,上层硅之间的最小间距为4 um。

( 10) 结构释放: 对上步硅片进行去胶,清洗等处理后,上层硅为保护层刻蚀中间氧化层,完成结构释放。

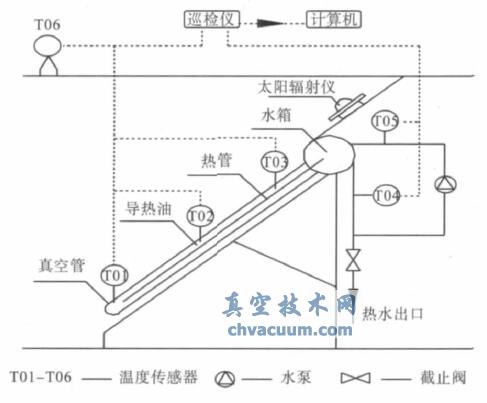

制备工艺步骤如图2 所示。

图2 制备工艺步骤

2、实验测试

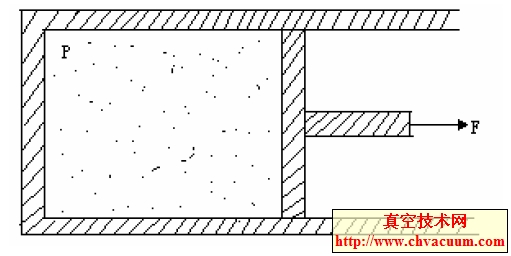

图3 测试原理图

利用自制的实验测试系统对本文设计、制备的SOI 基高g 值加速度传感器进行了实验测试分析,图3 是测试原理图。本测试系统是中科院上海微系统研究所针对其研制的压阻式加速度传感器自制的,由于加速度传感器结构特点及其理论模型存在差异,对系统测试进行了必要的修正。前期研究已表明,传感器在不同加速度载荷条件下,微梁的形变基本一致,在相同载荷间隔的条件下,微梁内部应力的变化间隔也基本保持不变,体现了良好的线性度。该加速度传感器结构的固有频率为479 kHz,在高达25 × 104g 加速度时,该微梁上的最大应力为544 MPa,远小于与硅材料的断裂强度0. 7~ 7 GPa,保证了该加速度传感器工作的可靠性。

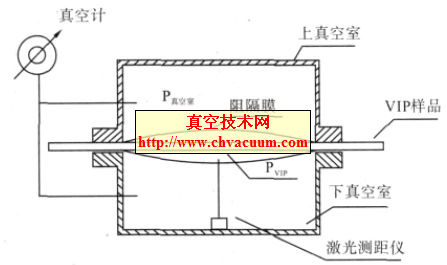

图4 给出了下降高度分别为75 和35 cm 时,对应加速度分析测试示例图。根据一系列的数据分析,得到输出电压与加速度的变化关系,如图5 所示,可见输出电压与加速度之间的线性度很好。根据实验数据分析可得,该高g 值加速度传感器的灵敏度是1.170 LV/ g 。

图4 下降高度分别为75 和35 cm 时,加速度测试示例图 图5 输出电压与加速度的变化关系

3、结束语

本文利用ICP 深硅刻蚀技术设计制备了一种SOI 基高g 值压阻式MEMS 加速度传感器,并进行了实验测试分析。实验表明,该高g 值压阻式加速度传感器输出电压与待测加速度之间的线性度很好,测试系统分析出的灵敏度是1.170 LV/ g,满足设计要求。此外,在制备刻蚀过程中还需注意:

(1) ICP 刻蚀中,由于刻蚀的不均匀性,使得圆片中部分结构刻蚀到氧化层,部分结构没有,为了使得整个圆片中的结构都刻蚀到氧化层,会造成先达到氧化层的结构过刻,由于刻蚀气体对材料的选择性,从而使得打到氧化层的刻蚀气体向两边扩散,造成footing 效应。

( 2) 氧化层的厚度如果过厚,利用干法刻蚀时需时间较久,从而刻蚀离子由于物理的轰击作用也会使得压敏电阻条被刻蚀掉一部分,因此需减小埋氧层的厚度。如果用湿法腐蚀则容易形成黏附效应,且背腔中易进腐蚀液损坏结构。