һ�����դ�������糣���ķ���

������90 nm �����ڵ㿪ʼ�������ӵ���SiON դ�����㱻�㷺�����Ƚ���CMOS �������졣��Ϊ��ͳSiO2 դ�������������ϣ�SiON դ������������нϸߵ���糣��������Ч���������դ������ԭ����դ�������е���ɢ�����������˻���(Post Nitridation Anneal, PNA)���Ʊ������ӵ���SiONդ�������һ����Ҫ���裬��Ҫ�������������˲��γ��ȶ�Si-N ����ͬʱ��������Χ��ͨ������Ķ���������Ӧ����SiO2/Si ��������ˡ�����ͨ���Դ�ͳդ���Ʊ�������PNA ��һ�����˻��յ��¶ȡ������Χ�����Ż����ṩ��һ��ͨ�����դ������ĵ�����������߽�糣���ķ�����ʵ�����ݱ������봫ͳ���Ʊ�������ȣ����ñ��������Ʊ���SiON դ�������е������������30%���ϣ�դ������̬�ܵ�ɿɼ���һ����������PMOS ������NBTI ����t0.1% ��t50%�ɷֱ����15.3% ��32.4%��

1������

���������ģ���ɵ�·(VLSI)���ش��ģ���ɵ�·(ULSI)�Ŀ��ٷ�չ���������ӹ�����������������Ҫ������MOS ���������ߴ��������ʱ����դ�������Ҫ�����һ�����Ե���ս��դ��������Ʊ������ǰ뵼�����칤���еĹؼ�������ֱ��Ӱ��;����������ĵ�ѧ���ԺͿɿ��ԡ�

����MOSFET�����Ĺؼ�����ָ�����������������������Ĵ�Сȡ����դ�����ݡ�դ��������դ������������ȣ���դ���ʺ�ȳɷ��ȡ���ˣ�ͨ������դ��������ͽ���դ���ʺ�Ⱦ������դ�����ݣ�������դ����SiO2 �ĺ�Ⱦͱ���ƽ�MOSFET ����������ߵ���Ҫ�ֶΡ�

���������뵼�弼������90 ����ʱ����������ͳ��������SiO2 ��ȵķ���������ǰ��δ�е���ս����Ϊ��ʱ��դ����SiO2 �ĺ���Ѿ��ܱ�(<20 �)��դ��©�����е������������Ѿ����������á�����SiO2 ��ȵĽ�һ�����ͣ�դ��©����Ҳ����ָ����ʽ������դ���ʺ��ÿ����2դ��©�����ͻ�����10 ������һ���棬դ����SiO2 դ���ʺ�ĵ�֮��������ʵ�Ũ���ݶȣ�����դ���ʺ�ȵIJ��Ͻ��ͣ�դ��������������ʻ��դ������ɢ����ĵ��л��߹̶���դ�����У����Ӱ����������ֵ��ѹ���Ӷ�Ӱ�����������ܡ���Ȼ������դ���ʺ�ȿ�����Ч����դ��©������դ�������ʵ���ɢ�����Ǿ����������������ת�ӳ�ʱ��ȹؼ�����Ҳ�����ۿۡ���������������դ��©���դ���ʺ��Ҫ���ϵ�ì�ܣ����ڴ�ͳ��SiO2 դ���ʶ��������رܵġ�

C = e0KA/t

�������У�C = դ������;e0 = �ڿ����еĵ�����;K= ���ϵĽ�糣��;A= դ�������;t= դ���ʺ�ȡ�

������դ�����ݵĹ�ʽ�����ǿ��Կ�����դ�����ݲ���ȡ����դ���������դ���ʺ�ȣ���ȡ����դ���ʵĽ�糣�����ʼ���դ���ʺ�Ȳ������դ�����ݵ�Ψһ��������ʹդ���ʺ�ȱ��ֲ��䣬���դ���ʵĽ��ϵ��K Ҳ�ɴﵽ����EOT ������դ�����ݵ�Ч������ˣ�������դ���ʵĽ��ϵ��K��Ϊ�˵���֮����

�������ֽΣ����դ���ʵĽ��ϵ���ķ��������������ࣺ

����һ���Dz���ȫ�µĸ߽��ϵ���IJ�����Ϊդ���ʣ��絪��������(HfSiON)�ȡ�������ȫ�²����漰��դ�����ϵ�ѡ��������ƥ�估�ع�ʴ�̵�һϵ�й��ռ������⣬��������������Խϳ���������������45 ����������������ͬʱȫ�²����ڼ���������ǰ�����нϴ���죬�������µijɱ����ߡ�

������һ�������Ա���SiO2 ��Ϊդ���ʣ�ͨ��SiO2����Ĥ����뵪ʹ֮��Ϊ���ܵ�SiON �����դ���ʵĽ��ϵ������Ϊ��ͳդ����SiO2 ��K ֵ��3.9��������Si3N4 ��K ֵ�ɴﵽ7��ͨ�����ӵ��Ķ��ٿ���ʵ�ֶ�SiON դ���ʽ��ϵ�����õ�Ŀ�ġ���ԭ�ӵIJ��뻹����Ч���������դ������ԭ����դ�����е���ɢ��ͬʱ���÷�����Ȼ����SiO2 ��Ϊդ���ʵ����壬�����ǰ�ڼ��������õ������Ժͼ����ԡ�

����Ŀǰҵ��ͨ����������Ҫ�ķ�����ʵ��SiO2�еĵ��������γ�SiON��

������һ�ַ�������SiO2 ������������ͨ��NO �Ⱥ������壬�Ӷ�������������ֱ�Ӳ��뵪�������ַ������ӵĵ������Ժ��ѿ��ƣ�������Ӧ�뵼��������Ҫ��

�����ڶ��ַ�������SiO2 ����������ɺ�����NO/N2O �Ⱥ������廷���н�һ���˻�İ취���ӵ������ַ�������ĵ�ԭ�����ۻ���SiO2 �����Ľ��洦���Ӷ��Թ����������ӵ�Ǩ���ٶȲ�������Ӱ�졣

���������ַ�������SiO2 ����������ͨ����������ʵ�ֵ����ӡ��÷�������ĵ�ԭ��Ũ�ȸߣ��������Ҫ�ֲ���դ���ʵ��ϱ����Զ��SiO2/ �������棬��Ŀǰ�뵼��ҵ��㷺���ܵ����դ���ʽ��ϵ���ķ���������幤����������ɣ�

����1)����ISSG(In-Situ Steam Generation)ԭλˮ����������������SiO2 ���ʲ�;

����2)����DPN(Decoupled Plasma Nitridation)��������������SiO2 �����в��ӵ�;

����3)����PNA(Post Nitridation Anneal)�����˻����ȶ�N ���Ӽ��������еĵ����������ˡ�

�����������Ʊ������У�����դ�����в���ĵ�ԭ��Ũ�ȸ�����Ҫ�ֲ���դ���ʵ��ϱ��棬��˶Ժ���PNA �����˻��յ��¶ȡ������Χ��ʱ���������ϸ���ƣ��Է�ֹ������������л������Ե�������ɵ�Ӱ��;���⣬PNA �ĸ����˻��ռ�������ɱ��浪ԭ�ӵĻӷ�������ʹ��ԭ�ӻ��������������ɢ����ɲ��ֵ�ԭ�Ӿۻ���SiO2/Si ���洦���Ӷ��Թ����������ӵ�Ǩ���ٶȲ�������Ӱ�졣

�������Ķ������Ʊ�������PNA �ĵ�һ�����˻��յ��¶ȡ������Χ�����Ż����ṩ��һ��ͨ�����դ�����ﵪ������������糣���ķ�����

2��ʵ��Ͳ��Է���

����ʵ�����300 mm��P ��(100)�辧Բ��������8��12Ω-cm������������ǰ�Թ�Ƭ������б���ϴ��դ���������AMAT Centura ACP �����˻��豸�Ʊ���

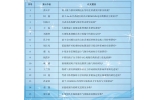

�������ȶԻ���ִ���������������ȴ������������γɾ����ȶ��;��ȵ�Ŀ���ȵ�SiO2 դ������;���ͨ���������嵪������������SiO2 դ��������е���ע�룬ʹSiO2 �еIJ���O ԭ����N ԭ��ȡ���γ�Si-N�����Ӷ�������SiO2 դ���������Ϊ����һ����Ũ�Ⱥͽ�糣����SiON դ������;Ȼ��ͨ������(1000��-1100��)�ʹ���������(��N2 ��) ��Χ��SiON դ��������е��������������������˲��γ��ȶ�Si-N �����Ӷ��γ��ȶ��ĵ������ͽ�糣��;����ڵ���(500��-800��) �ķ�Χ�¶�SiON դ�������������������������SiO2 / Si ���档

����դ�������Ⱥ͵���������Revera RVXTM1000X-Ray Photoelectron Spectroscopy �����ͱ�����դ���������̬����SEMILAB FAaSTR 350 �������ͱ�����PMOS ������NBTI (Negative Bias Temperature Instability)��������Agilent 4072 �������ͱ�����

3��ʵ��������

����դ���еĵ���Ҫ����DPN ����ͨ����������������SiO2 �����в��ӵ���ʵ�֣��䵪������Ҫ��DPN �Ĺ�������������������դ���еĵ��������������դ���Ľ�糣��������դ����©������ͬʱ��������Խ������������դ������ԭ����դ��������ɢ������ҲԽǿ����ˣ��Ż����й������������դ���еĵ�������Ϊһ����Ϊ���е�Ҫ��

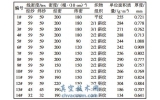

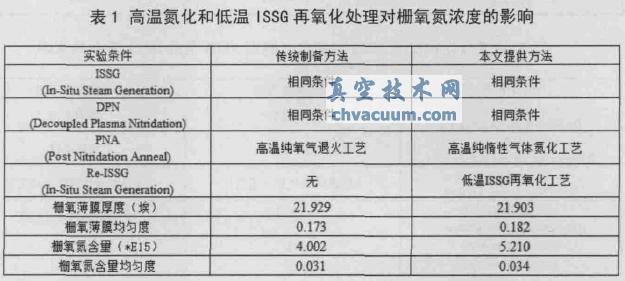

������1 Ϊ���ø��µ����͵���ISSG ������������դ����Ũ�ȵı仯��ʵ�����ݱ������ڱ�����ͬDPN ���������£���������õ�һ���´������˻���������ȣ�������µ����͵���ISSG ������������դ���е�Ũ�ȿ������30%���ϡ�ʵ�������������´������������������Ӳ��ӵ����ɼ��ļ��ʣ������ڴٽ�դ���е��ļ��Ϻ��ȶ�������ʵ�������й������������դ�������糣���������糣�����о�ȷ���õ�Ŀ�ġ�

����DPN ���������ڶ�դ���ʽ��е����ӵ�ͬʱ���������ӵ���ײ���դ���ʲ������ˡ�����65 �������¼����ڵ���ԣ�դ���ʺ����Խϱ������������еĸ������Ӵ�դ����ֱ�����˹����������Σ�ռ������ӣ�������øĽ��������Խ����

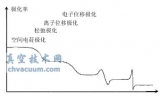

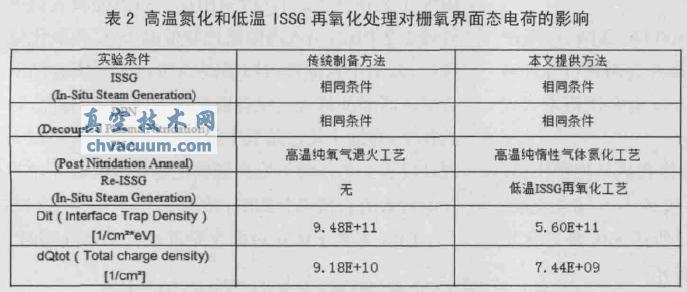

��������ͨ�����ºʹ���������(��N2 ��)��Χ��SiON դ��������е�������������DPN ��������ɵľ������˲��γ��ȶ�Si-N �����Ӷ��γ��ȶ��ĵ������ͽ�糣��;Ȼ���ڵ��µ�������Χ�¶�SiON դ���������ISSG ����������������ԭ������ǿ������������SiO2/Si �Ľ���ȱ�ݣ�������2 ��ʾ�����ݱ�������������õ�һ���´������˻���������ȣ�������µ����͵���ISSG ������������դ������Si/SiO2 ����̬�õ�����Ч�ĸ��ƣ������̬�ܵ�ɼ�����һ����������ʵ�������������µ����͵���ISSG ��������������Ч����դ���Ľ���̬��

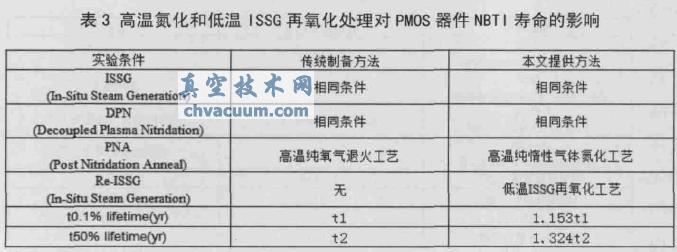

������ǰ��������DPN ���պ�������µ����͵���ISSG ������������õ���դ�����ﱡĤ����ȱ���٣�����̬��Ҳ�Ƚ�С�������ﱡĤ�������Ƚϸߡ���3 Ϊ���µ����͵���ISSG ������������PMOS����NBTI ������Ӱ�졣���ݱ�������������õ�һ���´������˻���������ȣ�������µ����͵���ISSG ������������դ�������0.1% ��t50%�ֱ������15.3%��32.4%��ʵ�������������µ����͵���ISSG ��������������Ч����PMOS ������NBTI ���ܡ�

4������

��������ͨ���Դ�ͳդ���Ʊ�������PNA ��һ�����˻��յ��¶ȡ������Χ�����Ż����ṩ��һ��ͨ�����դ�����ﵪ������������糣���ķ��������ñ����ṩ�ķ����Ʊ���SiON դ�����㲻�������ȶ��ĵ���������������Ч���դ�����ﵪ����30%���ң��Ӷ�ʹ���Ʊ���դ��������нϸߵĽ�糣����ʵ���˶�SiON դ���ʽ��ϵ����ȷ���õ�Ŀ�ġ�ͬʱ�����ñ��������Ʊ���SiON դ���������̬�ܵ�ɿɼ���һ����������PMOS ������NBTI ����t0.1% ��t50%�ɷֱ����15.3% ��32.4%��